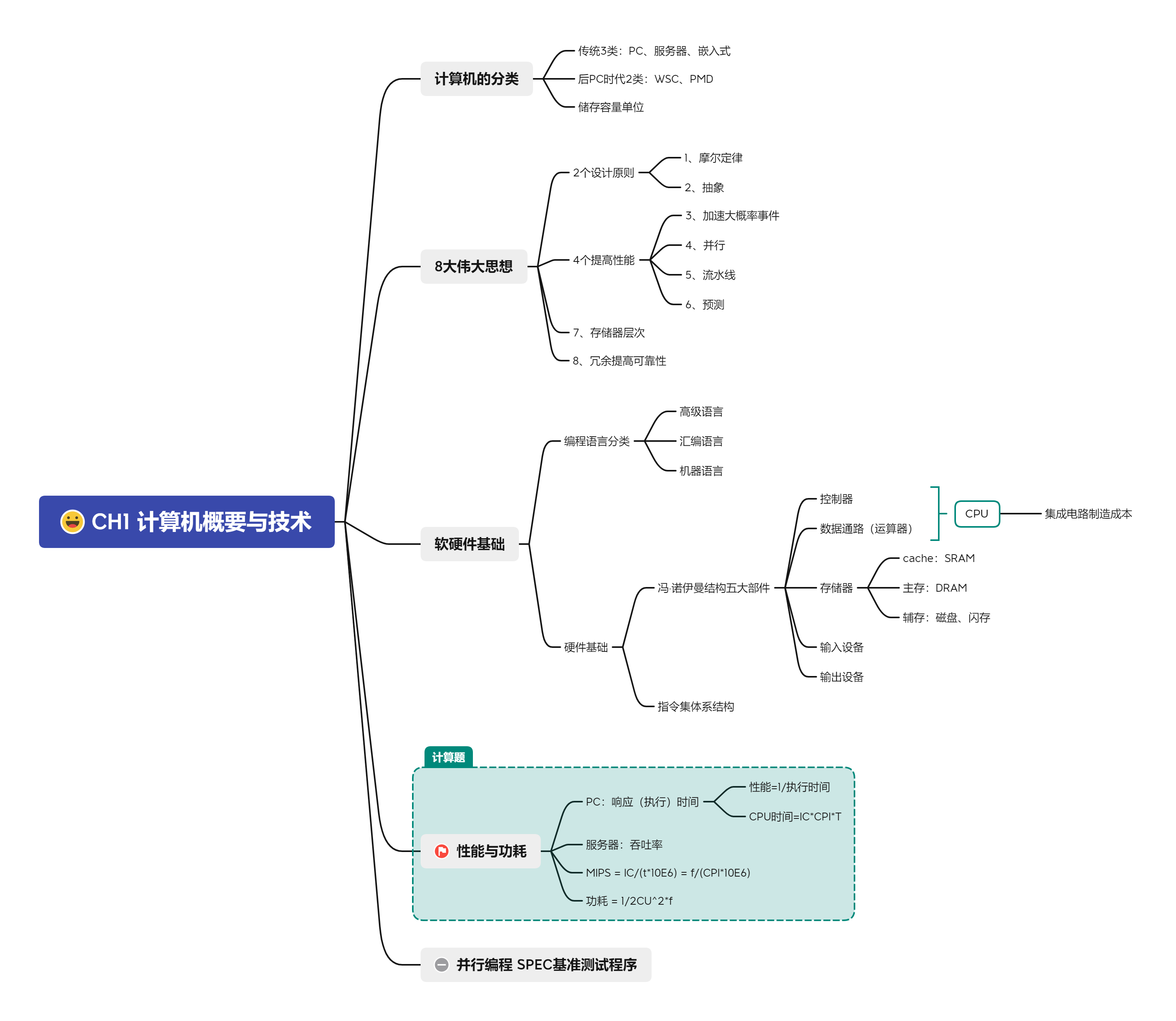

复习题

- PC和服务器分别更看重哪项性能评价指标?

- CPU经典性能公式计算的是什么指标?公式是什么(注意有两个联系密切的版本)?

- 我们是如何得出经典性能公式的?

- 哪四个东西会通过影响性能公式中的某些项,从而影响性能?

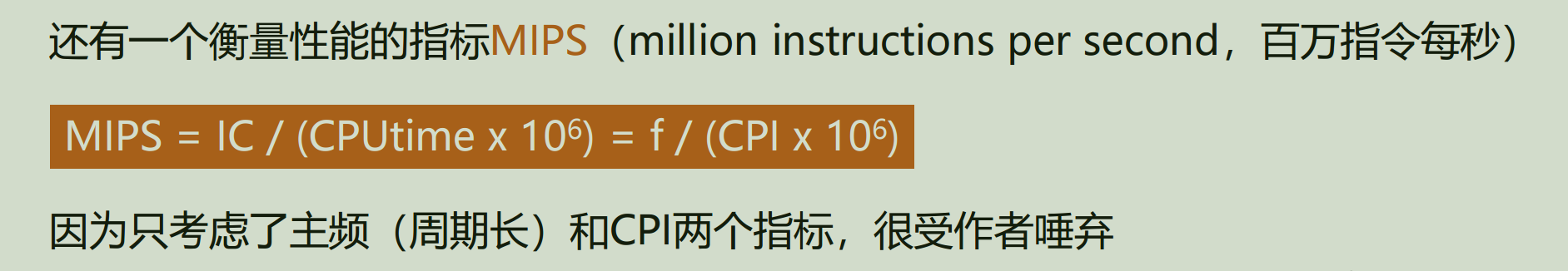

- MIPS怎么计算?这个性能指标为什么不靠谱?

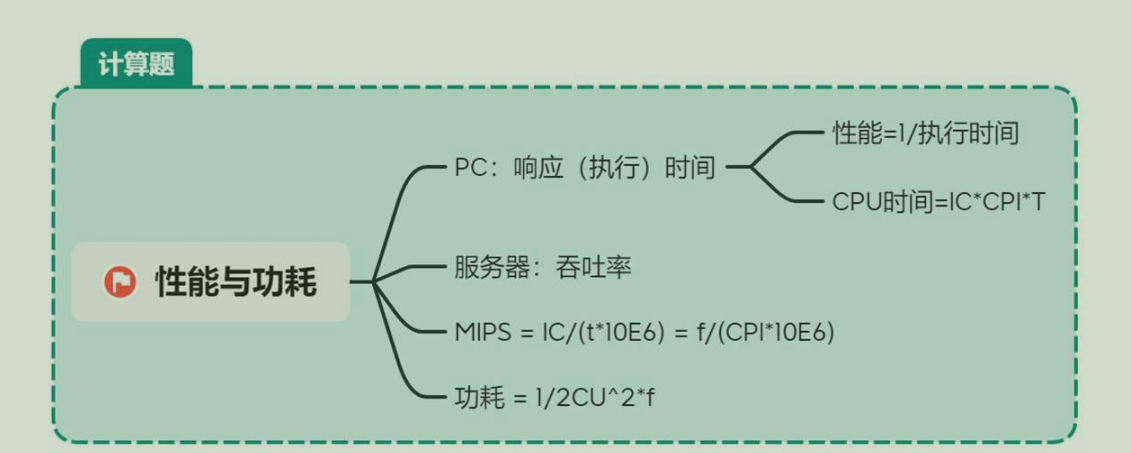

性能与功耗

评价性能的指标

PC和服务器分别更看重哪项性能评价指标? #card

- 个人计算机:看重响应时间(又称执行时间):任务从开始到完成的时间

- 响应时间:在操作系统中作为进程的执行的时间度量单位

- 服务器:看重吞吐率:单位时间内完成的任务数量

例题:

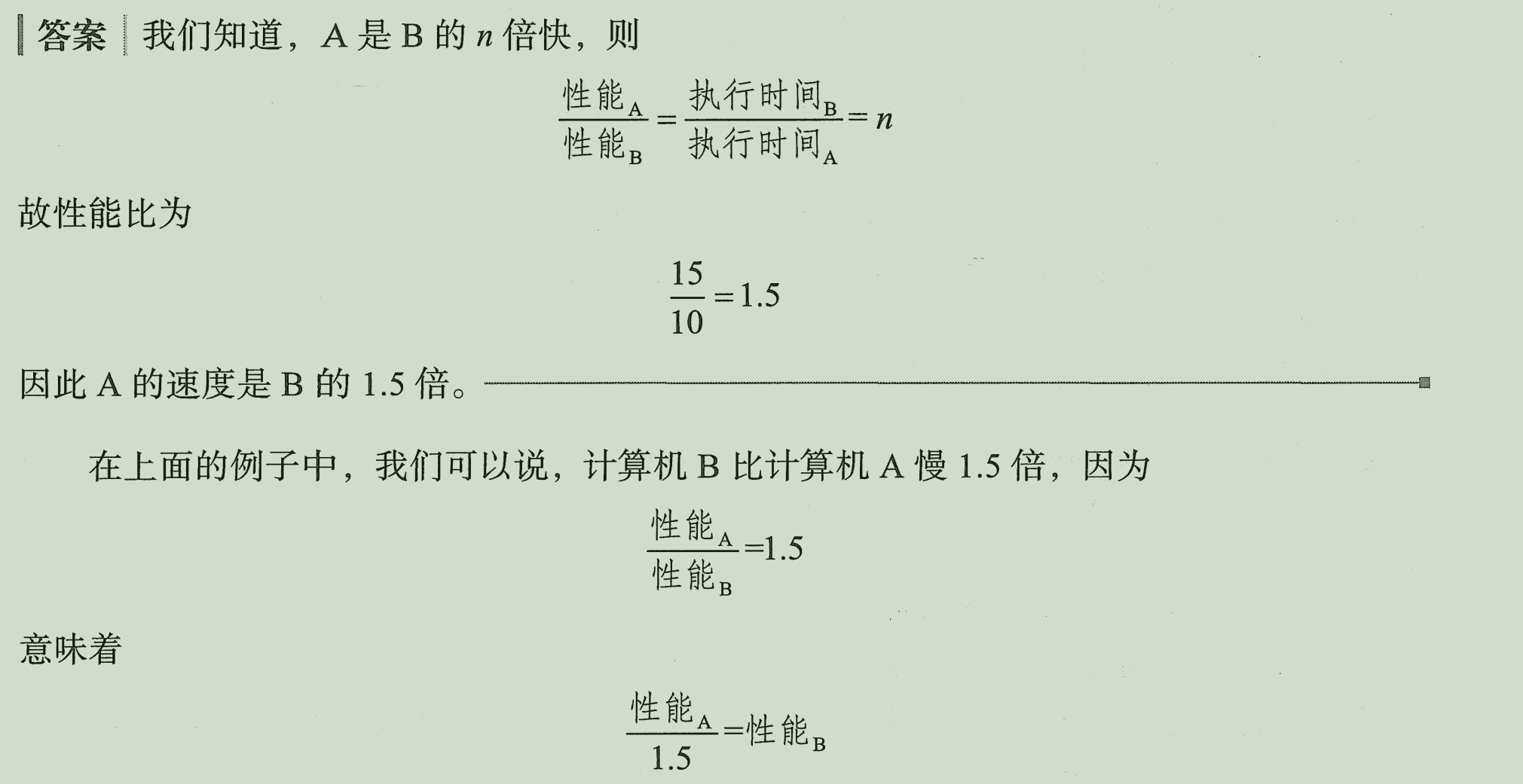

计算机A的性能是计算机B的几倍?→计算机A的执行时间是B的几分之一?

e.g. 运行同一个程序,计算机A用15秒,计算机B用10秒,谁的性能更高?它的性能比另

外一台高多少? #card

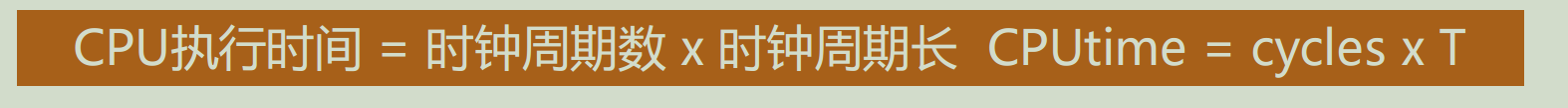

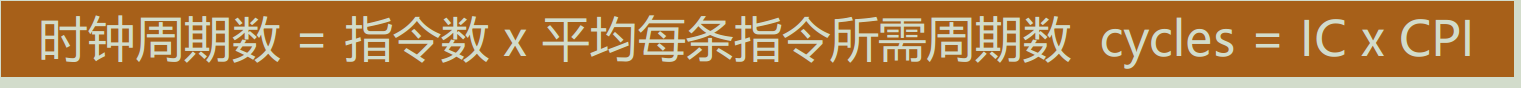

CPU经典性能公式

如果我们要测量一个地球有多长,我们应该规定1m有多长(单位)

地球有多少个单位(数量)

时钟周期长

- 正如我们对于PC的性能测试:对于响应时间的测试。

- 这个时间我们需要最小的标准,也就是时钟周期,这是机器最小的周期单位。

- CPU时钟周期长度T(CPU干任何事的时间都是一个时钟周期的整数倍)

- 一般通过时钟频率来计算时钟周期长

干一件事,即执行一个程序,需要多少个时钟周期?

- 一般通过时钟频率来计算时钟周期长

时钟周期数

任何程序都要以机器语言指令的形式,才能被计算机看懂

所以,执行程序本质上就是执行机器指令!

不同机器指令需要的周期数不尽相同

我们使用一个统计平均值来作为平均周期数CPI

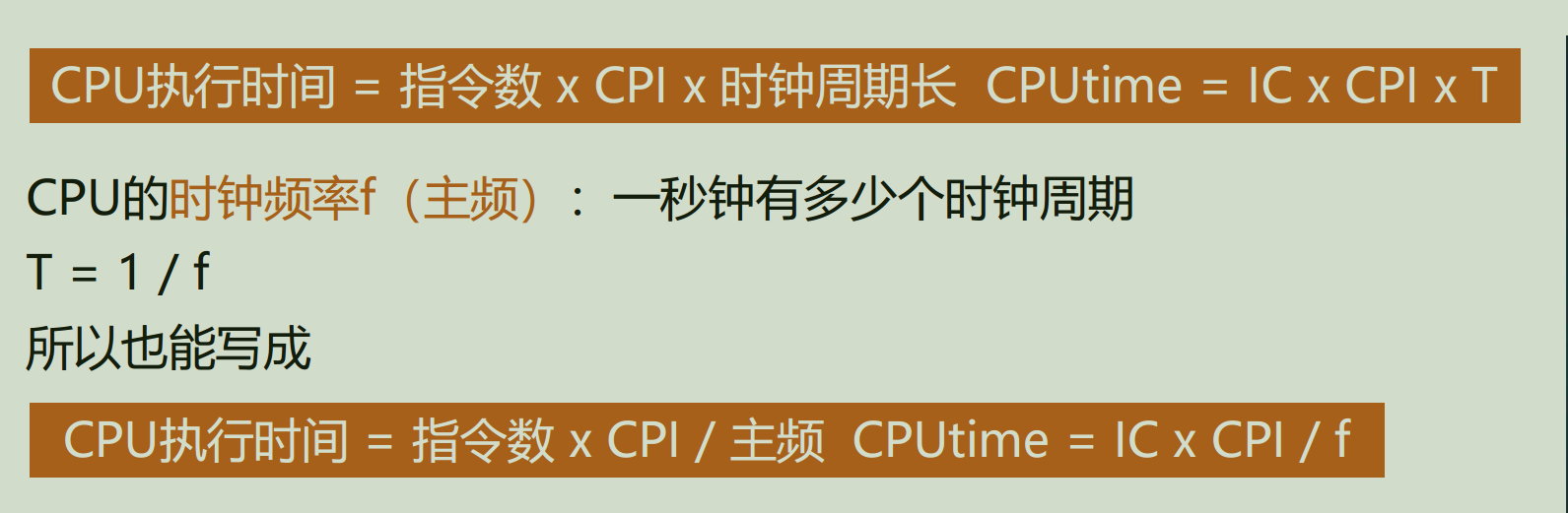

CPU执行时间公式 #card

例题:

e.g. 主频为4GHz的CPU,每个时钟周期的长度是多少秒?

某程序共有3亿条指令,其中1亿条的CPI为3,2亿条的CPI为6,整个程序的CPI是多少?

该CPU执行这个程序需要多长时间? #card

- 计算每个时钟周期的长度:

主频为 4GHz,即每秒有 40 亿个时钟周期。因此,每个时钟周期的长度为:

- 计算整个程序的 CPI:

程序共有 3 亿条指令,其中 1 亿条的 CPI 为 3,2 亿条的 CPI 为 6。整个程序的 CPI 可以通过加权平均来计算:

- 计算执行程序所需的时间:

该 CPU 执行这个程序需要的时间可以通过以下公式计算:

代入已知值:

因此,该 CPU 执行这个程序需要 秒。

CPU经典性能公式为什么靠谱

- 经典性能公式考虑了指令数IC、平均每条指令需要周期数CPI、时钟周期长度T(也就是主频f的倒数)全部三个因素

- 使用CPU执行时间这个靠谱的指标来衡量性能

- 使用什么编程语言和编译程序、采取什么算法,影响指令数和CPI两个因素;采用什么指令集体系结构,影响指令数、CPI、主频全部三个因素。它们都会影响CPU性能。

功耗

在移动设备和WSC中,电能是关键资源

但随着CPU集成度越来越高,晶体管的数量剧增,功耗越来越大、散热越来越难

CMOS(互补型金属氧化半导体)是当前占统治地位的集成电路技术

其中,晶体管的能耗主要来自动态能耗,即晶体管打开/关闭的短暂动态过程

即0→1或1→0的过程

一个晶体管经历一次0 → 1 → 0或1 → 0 → 1的开关过程(在开关过程中使用了最多的能量)

能耗 = 负载电容 x电压²

开关频率与CPU主频相关

所以,功耗公式为 #card

并行化 基准测试程序

CPU设计面临功耗墙问题

从2002年起,单核处理器性能增长速度从每年约52%下降到22%,功耗问题“功不可没”

因此,从单处理器向多核处理器转变成为近年计算机提升性能的主要手段

同时,硬件变成了多处理器

要求程序员重写代码去支持CPU的并行(同时执行)特性

显式并行编程应运而生,但仍有很多需要克服的问题

设有一个单核处理器A,还有一个每个核心都和A相同的四核处理器B,

它们运行同一个程序,B的CPU时间能减少到A的1/4吗?

)